# Switched-Current Techniques: An Overview of Cumulative SI-Related Errors on Dynamic and Static Performances of 2<sup>nd</sup> Order LP-∑∆Ms

Karim ABBES, Naoufel Gueddah and Mohamed MASMOUDI

Electronics, Microtechnology and Communication (EMC) Research Group University of Sfax, National Engineers School of Sfax BP 1173, 3038, Sfax, Tunisia karim.abbes@enis.rnu.tn

**Abstract**: We present in this work a systematic analysis to identify  $\underline{Sigma}$   $\underline{Delta}$   $\underline{Modulators}$  ( $\Sigma\Delta Ms$ ) non-idealities, such as charge injection error, Input/Output conductance ratio error and settling time error. A physical mechanism behind  $\underline{S}$  witched  $\underline{C}$  urrent (SI) errors is proposed. In the first time, errors mentioned above are treated separately and a behavioural model of SI cell is derived for each non-ideality. In the second time, we propose a behavioural model of Non-inverting Lossless Integrator. For typical variations of SI-related errors, simulations have been made using Matlab/Simulink. Finally we present their influences on both dynamic and static performances of the 2nd order SI  $\underline{Low}$   $\underline{Pass}$   $\underline{\Sigma}\Delta Ms$  (SI-LP $\underline{\Sigma}\Delta Ms$ ).

**Keywords:** Analog/Digital Converter, Switched Current technique, Sigma-Delta Modulator, error mechanisms, Dynamic and Static Performances.

#### 1. Introduction

The staggering scaling-down of  $\underline{C}$  omplementary  $\underline{M}$  etal  $\underline{O}$  xide  $\underline{S}$  emiconductor (CMOS)  $\underline{V}$  ery- $\underline{L}$  arge- $\underline{S}$  cale Integration (VLSI) technologies and the tendency towards  $\underline{S}$  ystems  $\underline{O}$ n  $\underline{C}$  hip (SOC) are prompting the development of new digital telecommunication devices spanning the portable gadgets of nowadays (cellular phone, smart phone, tablet computer...). SI technique has been adopted in many applications (e.g. filtering [1, 2], current differentiation [3], Sigma Delta modulation [4],  $\underline{D}$  igital to  $\underline{A}$  nalog  $\underline{C}$  onverters (DACs) and  $\underline{A}$  nalog to  $\underline{D}$  igital  $\underline{C}$  onverters (ADCs) [5, 6, 7, 8]).  $\underline{\Sigma}$  AMs are very suited to implement high-resolution and robust (lower sensitivity to circuitry imperfections) ADCs, not only by increasing the oversampling ratio (a sampling frequency much larger than the Nyquist frequency) but also by pushing the quantization noise out of the band of interest. Furthermore, oversampled SI  $\underline{\Sigma}$  AMs have gained much popularity for their high-speed, low consumption and low supply voltage compared to the  $\underline{S}$  witched- $\underline{C}$  apacitor (SC) technique [9, 10, 11, 12]. The use of such technique facilitates the integration of a whole system into a mixed signal chip. The analog portion of these chips must feature the required analog performance level in VLSI standard, what has motivated exploring analog design technique compatible with CMOS process [13, 14, 15].

Several works have been focused on identifying and modeling non-idealities in both SI and SC techniques in order to get a behavioural model of these cells. The non-ideal behavioural model has been made only at memory cell level [2, 9, 22, 23, 24]. N. Khitouni et al. and M. Loulou et al. respectively [16] and [17], have developed a mathematical model of charge injection phenomena. By using a continuous and physical formulation based on the Enz-Krummenacher-Vittoz model (EKV), A. Dei et al. [18] have developed a compact behavioural model of the MOS analogue switch for charge injection analysis. According to W. Ming Koe et al. [19], a better understanding of non-idealities in switched-capacitor circuits on sigma-delta modulators can be achieved if each of these non-idealities is studied separately.

In this work, we will study the cumulative effect of SI-related error on dynamic and static SI-LP $\Sigma\Delta M$  performances. The analysis will be focused on 1-bit  $2^{nd}$ -LP $\Sigma\Delta M$ . This modulator

Received: October 26<sup>th</sup>, 2011. Accepted: December 8<sup>th</sup>, 2011

is easy to understand and simple to design. Nevertheless, this study can be extended to other architectures such as multi-stage cascade modulators [7], since the integrator represent the main block in this kind of architectures.

The paper is organized as follows; A briefly review of  $\Sigma\Delta M$  principle is presented in section 2. In section 3, we analyse the effect of isolated non-idealities on transfer function of SI memory cell. Section 4 describes the cumulative error effect on the transfer function of the Non-Inverting Lossless Integrator. The impact on the dynamic and static performances on LP-SI $\Sigma\Delta M$  is carried out in Section 5. Lastly, we conclude this paper in section 6.

#### 2. Modulator Architecture Overview

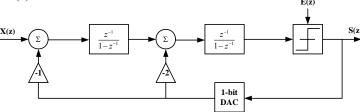

Figure 1 shows the Z-domain of 1-bit  $2^{nd}$ -LP $\sum \Delta M$  block diagram. The output modulator is given by Equ. 1 if we assume that the quantized error is modeled as a white noise [7]:

$$S(z) = STF(z) \cdot X(z) + NTF(z) \cdot E(z)$$

(1)

Where, X(z) and E(z) are respectively the z-transform of the input signal and the quantization noise source. The <u>Signal Transfer Function</u> (STF) and the <u>Noise Transfer Function</u> (NTF) are given by:

$$STF(z) = z^{-2} \tag{2}$$

$$NTF\left(z\right) = \left(1 - z^{-1}\right)^{2} \tag{3}$$

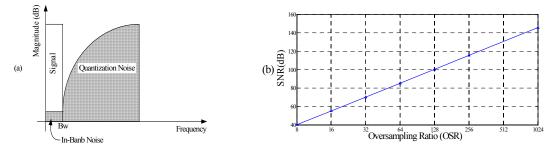

For physical frequencies,  $z = e^{j\omega T}$ , and  $\omega T$  much smaller than unity to correspond to the highly oversampled situation, the magnitude response of NTF can be very well approximated by  $\omega$ . Thus at low frequencies, the quantization noise is made insignificant, whereas at high frequencies it is greatly increased. We can therefore conclude that the NTF is a high-pass function and the noise power is shaped to frequency region where the input signal is not located. Subsequent filtering can then separate the input signal from the quantization noise as illustrated in Figure2(a).

Figure 1. 1-bit  $2^{nd}$ -LP $\sum \Delta M$  Architecture under study.

Figure 2. (a) Filtering function of 2<sup>nd</sup>-LPSDMs, (b) SNR(dB) vs. oversampling ratio OSR

The in band quantization noise power is given by Equ. 4:

$$P_{Q} = \int_{0}^{Bw} 2 \cdot E \cdot \left| NTF(f) \right|^{2} df = \frac{\Delta^{2}}{12 \cdot \pi \cdot OSR} \sin\left(\frac{2\pi}{OSR}\right) \cdot OSR + 6\pi - 8 \cdot \sin\left(\frac{\pi}{OSR}\right) \cdot OSR$$

(4)

Where, <u>Band</u> wide (*Bw*) is the signal band,  $\Delta$  is the quantization noise step, and  $OSR = \frac{f_s}{2 \cdot Bw}$  is the oversampling ratio with  $f_s$  is the sampling frequency.

Consider a sinewave input signal and N is the quantizer resolution, the maximum full-scale input signal power is found to be,

$$P_{s} = \frac{\left(\frac{\Delta \cdot 2^{N}}{2}\right)^{2}}{2} \tag{5}$$

And then the Signal to Noise Ratio (SNR) is given as below:

$$SNR_{dB} = 10 \cdot \log_{10} \left( \frac{P_s}{P_Q} \right) = 10 \cdot \log_{10} \left( \frac{6\pi M}{\sin \left( \frac{2\pi}{OSR} \right) \cdot OSR + 6\pi - 8 \cdot \sin \left( \frac{\pi}{OSR} \right) \cdot OSR} \right)$$

(6)

Equ. 7 gives the output Effective Number Of Bit (ENOB).

$$ENOB = \frac{SNR_{dB} - 1.7}{6.02} \tag{7}$$

In this scenario presented by equations (6) and (7), the resolution increases with *OSR* at rate of  $\approx 2.5bit / octave$  as illustrated in Figure 2(b).

### 3. Study of Isolated Error Mechanism of Si CELL

Several alternatives to analyse the non-idealities behaviour have been described in the literature [14, 25, 26]. These errors are responsible for SNR degradation of  $\Sigma\Delta$ Ms. The main

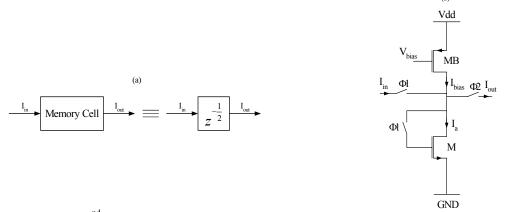

Figure 3. Ideal 2<sup>nd</sup> generation SI memory cell, (a) z-domain building bloc, (b) transistor level.

errors related on the SI memory cell are: output-input conductance ratio, charge injection and settling time errors. A switched current memory cell performs the function of a current copier, and it is ideally modeled by a delay line of a half clock period as shown in Figure 3(a). In this paper, the study is based on 2<sup>nd</sup> generation memory cell presented in Figure 3(b). In this kind of cell, the same transistor is used to implement both the sink and source currents. Thus, it does not exhibit mismatch errors [24].

# A. Output/Input conductance ratio error

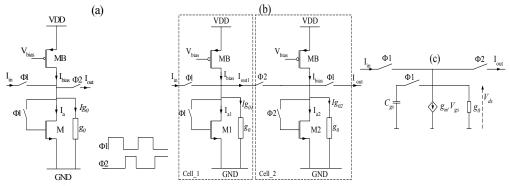

As it shown in Fig.4 (a), the memory cell can be modeled as an ideal memory transistor M in parallel with a conductance  $g_0$  given by Equ. 8. [9, 14, 25].

$$g_0 = g_{ds} \frac{C_{gd}}{C + C_{gd}} g_m \tag{8}$$

Where  $g_{ds}$  is the output conductance of memory transistor, C is the memory capacitor,  $g_m$  is the transconductance of the memory transistor M and  $C_{gd}$  is the drain gate parasitic capacitance.

This conductance is due to two main effects:

- Firstly, the channel length modulation effect of both memory transistor M and the bias one MB.

- Secondly, the charge injected into the memory capacitance C when the gate of the memory transistor held open. This leads to a disturbance of the gate-source voltage and therefore an error in the drain current  $I_a$ .

We consider cascaded memory cell shown in Figure 4(b) and taken the equivalent small signal model shown in Figure 4(c). On phase  $\Phi I$ , memory transistor MI is diode connected, therefore

for small signal

$$V_{ds} = V_{gs} + \frac{I_{in}(n-1)}{g_m}$$

and  $I_{al}$  is given by Equ. 9.

$$I_{a1} = I_{bias} + I_{in} (n-1) - I_{g_{01}} = I_{bias} + I_{in} (n-1) \left( 1 - \frac{g0}{gm} \right) - V_{gs} \cdot g_0$$

(9)

On phase  $\Phi 2$ , the drain voltage of MI is determined by the gate voltage of M2 i.e.

$$V_{ds1} = V_{gs2} = V_{gs} + \frac{I_{out1} \left( n - \frac{1}{2} \right)}{g_m} \quad \text{and Equ. 10 gives the output current } I_{out1} \left( n - \frac{1}{2} \right) .$$

$$I_{out1}\left(n - \frac{1}{2}\right) = I_{bias} - I_{a1} - I_{g_{02}} = -I_{in}\left(n - 1\right)\left(1 - \frac{2g_0}{g_m}\right) \approx -\frac{I_{in}\left(n - 1\right)}{1 + \frac{2g_0}{g_m}} \tag{10}$$

We notice, after making z-transformation, that the transfer function of the memory cell,  $H_{\varepsilon_a}(z)$ , can be written by Equ. 11:

$$H_{\varepsilon_{g}}(z) = \frac{I_{out1}(z)}{I_{in}(z)} = \frac{-z^{-\frac{1}{2}}}{1 + \frac{2g_{0}}{g_{m}}} = \frac{H_{i}(z)}{1 + \varepsilon_{g}}$$

(11)

Where  $H_i(z)$  is the ideal transfer function of the SI memory cell and  $\varepsilon_g = \frac{2g_0}{g_m}$  is the I/O

conductance error

Figure 4. 2<sup>nd</sup> generation SI memory cell. (a) With output-input conductance error. (b) Cascaded memory cells. (c) Small signal model.

#### B. Settling time error

SI circuits are based on charging and discharging the gate capacitance of the memory transistor. During the sampling phase, the input current witch is applied to the memory cell charges or discharges the gate-source capacitance  $C_{gs}$ . If at the end of the sampling period,  $C_{gs}$  has not been charged or discharged to the final value, errors occur in the memorized current  $I_a$ . This error is represented by  $\varepsilon_s$  in SI context.

In this analysis, we consider the linear model of SI memory cell presented in Figure 3(b) with only  $\varepsilon_s$  error. During the clock phase  $\Phi I$  the memory transistor is diode-connected and the drain current  $I_a$  increases from its previous level  $I_a(n-1)$  towards a new level given by Equ. 12.

$$\overline{I}_{a}(n) = I_{bias} + I_{in}\left(n - \frac{1}{2}\right) \tag{12}$$

Assuming the cell is linear and so  $I_a$  reaches a final value  $I_a(n)$  given by

$$I_{a}(n) = I_{a}(n-1) + \left[ F_{a}(n) - I_{a}(n-1) \right] (1 - \varepsilon_{s})$$

$$(13)$$

Where  $\mathcal{E}_s = e^{\frac{\tau}{2\tau}}$  is the settling time error. The time-constant  $\tau = C/g_m$  represents the effective time constant of the memory cell occur on clock phase  $\Phi I$  [27].

During the next phase  $\Phi 2$ ,  $I_{out}(n)$  is given by Equ. 14. And during previous phase  $\Phi 2$ , the output current is given by Equ. 15.

$$I_{out}(n) = I_{bias} - I_a(n) \tag{14}$$

$$I_{out}(n-1) = I_{bias} - I_a(n-1)$$

$$\tag{15}$$

The output SI cell current is expressed from Equ.12 to Equ 15 by:

$$I_{out}(n) = \varepsilon_s I_{out}(n-1) - (1 - \varepsilon_s) I_{in}\left(n - \frac{1}{2}\right)$$

(16)

The transfer function with settling time error,  $\varepsilon_s$ , is given by:

$$H_{\varepsilon_s}(z) = -z^{-\frac{1}{2}} \frac{1 - \varepsilon_s}{1 - \varepsilon_c z^{-1}} = H_i \frac{1 - \varepsilon_s}{1 - \varepsilon_c z^{-1}}$$

$$\tag{17}$$

We notice that settling time gives rise to an additional multiplicative error term in the overall transfer function.

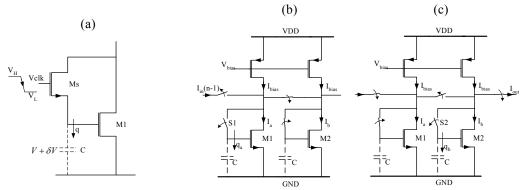

#### C. Charge injection error

Referring to Figure 5(a), switches are realized through MOS transistors operating alternatively in linear and cut-off region. When switch  $M_s$  goes off, channel charges flow out of its drain, substrate and source. Part of this charge is dumped to the memory capacitance C. In addition, due to the overlapping capacitance  $C_{ol}$  and the channel capacitance  $C_{ch}$ , the memory gate-source voltage  $V_{gs}$  of M vary [9, 14].

Figure 5. Cascaded SI memory cell. (a) SI memory cell with a switch transistor. (b) Phase  $\Phi 1$ . (c) Phase  $\Phi 2$ .

We consider tow cascaded memory cell shown in Figure 5(b). During phase  $\Phi 1$  of period (n-1) Ts, where Ts is the sampling period, the drain current in M1 is:

$$I_{a}(n-1) = I_{bias} + I_{in}(n-1)$$

(18)

At the end of phase  $\Phi I$ , switch SI opens and its charge  $q_a$  causes an error  $\delta I_a$  in the current stored during the next phase  $\Phi 2$ . The expressions of stored current in MI and M2 are given respectively by Equ. 19 and Equ. 20.

$$I_a\left(n - \frac{1}{2}\right) = I_a\left(n - 1\right) - \delta I_a \tag{19}$$

$$I_{b}\left(n - \frac{1}{2}\right) = 2I_{bias} - I_{a}\left(n - \frac{1}{2}\right) = I_{bias} - I_{in}\left(n - 1\right) + \delta I_{a}$$

(20)

At the end of clock phase  $\Phi 2$ , shown in Figure 5(c), switch S2 opens and its charge  $q_b$  causes an error  $\delta I_b$  in the current stored during the next phase  $\Phi I$ .

$$I_b(n) = I_b\left(n - \frac{1}{2}\right) - \delta I_b = I_{bias} - I_{in}(n-1) + \left(\delta I_a - \delta I_b\right)$$

(21)

As reported in [9] and [14],  $(\delta I_a - \delta I_b)$  is given by:

$$\delta I_a - \delta I_b = 2\varepsilon_q I_{in} (n-1), \qquad \varepsilon_q = \frac{K_A}{V_{os} - V_T} - K_B$$

(22)

Where  $K_A$  and  $K_B$  are respectively the coefficient of the independent and the dependent parts of the signal, which are given by:

$$K_{A} = \alpha \frac{C_{ch}}{C} \left( V_{H} - \left( 2 + \frac{\gamma}{3} \right) V_{gs} - V_{T} \right) + \left( V_{H} - V_{L} \right) \frac{C_{ol}}{C}$$

$$K_{B} = 2\alpha \left( 1 + \frac{\gamma}{3} \right) \frac{C_{ch}}{C}$$

(23)

With  $V_T$  is the threshold voltage of switch transistor  $M_s$ ,  $\gamma$  is bulk-threshold parameter,  $\alpha$  determines the portion of the channel charge that flows to the memory capacitance C

Substituting Equ. 22 in Equ. 21, for  $I_{out}(n) = I_{bias} - I_b(n)$ , and after performing the z-transform, the transfer function of the pair memory cell yields:

$$\left[H_{\varepsilon_q}(z)\right]^2 = \left(1 - 2\varepsilon_q\right)z^{-1} \tag{24}$$

And then, the transfer function of single SI cell with charge injection error,  $_q$ , can be written as:

$$H_{\varepsilon_q}(z) = \frac{-z^{-\frac{1}{2}}}{1+\varepsilon_q} = \frac{H_i(z)}{1+\varepsilon_q}$$

(25)

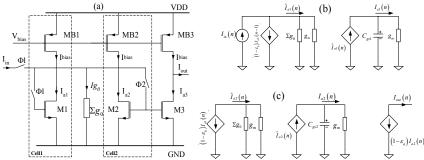

#### 4. Cumulative Errors Effect on The Non-Inverting Lossless SI Integrator

The isolated influence of main SI errors on the transfer function of SI memory cell has been analysed in the previous section. In this section, analysis will be extended from the memory cell to another higher hierarchical level circuit such as integrator.

We consider the SI realization of Non-Inverting Lossless Integrator shown in Figure 6(a). On clock phase  $\Phi I$  the small signal equivalent circuit is shown in Figure 6(b). The steady state drain current  $\hat{I}_{a1}$  of memory transistor MI is given by:

$$\hat{I}_{a1}(n) = (1 - \varepsilon_g)(I_{in}(n) - (1 - \varepsilon_q)I_{a2}(n-1))$$

(26)

Equ. 27 presents the influence of the settling time error on the memory transistor drain current.

$$I_{a1}(n) = \varepsilon_s I_{a1}(n-1) + (1-\varepsilon_s) \hat{I}_{a1}(n)$$

(27)

On clock phase  $\Phi 2$  the small signal equivalent circuit is shown in Figure 6(c). The steady state drain current  $\hat{I}_{a2}$  of memory transistor M2 is given by:

$$\hat{I}_{a2}(n) = -(1 - \varepsilon_g)(1 - \varepsilon_q)I_{a1}(n) \tag{28}$$

Due to settling time error,

$$I_{a2}(n) = \varepsilon_s I_{a2}(n-1) + (1 - \varepsilon_s) \hat{I}_{a2}(n)$$

(29)

Assuming that the current mirror is ideal, the output current will be:

$$I_{out}(n) = -(1 - \varepsilon_a) I_{a2}(n) \tag{30}$$

From Equ. 26 to Equ. 30 and after performing z-transform, the transfer function of the Non-Inverting Lossless Integrator with all errors mentioned in the above section ( $\varepsilon_g$ ,  $\varepsilon_q$  and  $\varepsilon_s$ ) is expressed by Equ. 31.

$$H_{\varepsilon_{g},\varepsilon_{q},\varepsilon_{s}}^{\text{int}}(z) = \frac{\left(1-\varepsilon_{g}\right)^{2} \left(1-\varepsilon_{q}\right)^{2} \left(1-\varepsilon_{s}\right)^{2} z^{-1}}{1-\left(2\varepsilon_{s}+\left(1-\varepsilon_{g}\right)^{2} \left(1-\varepsilon_{q}\right)^{2} \left(1-\varepsilon_{s}\right)^{2}\right) z^{-1}+\varepsilon_{s}^{2} z^{-2}}$$

(31)

By nullifying errors ( $\varepsilon_g$ ,  $\varepsilon_q$  and  $\varepsilon_s$ ) in Equ. 31, we obtain the ideal transfer function of the integrator shown in Figure 1. Furthermore, all error mechanisms contribute as a gain error, but the settling time error is the only one that changes the poles of the SI integrator transfer function.

After identifying the error mechanisms of SI memory cell and SI integrator, next section will be focused on the effect of these errors on 2<sup>nd</sup> order SI-LP M dynamic and static performances.

Figure 6. Non-inverting Lossless Integrator. (a) SI schematic. (b) Small signal equivalent circuit during  $\Phi I$ . (c) Small signal equivalent circuit during  $\Phi 2$

# 5. Non-Idealities Effects on 2<sup>nd</sup> Order Lp-Si∑∆M

This section analyses the influence of the fundamental error mechanisms, detailed in the previous sections, on the performances of  $2^{nd}$  order LP-SI $\Sigma\Delta M$ . Analysis will be focused on: firstly, the separately effect of each non ideality by keeping one error and nullifying the rest (e.i.  $\varepsilon_g = \varepsilon_q = 0$ ,  $0 < \varepsilon_s < 5\%$ ) (Equ. 32 and Equ. 33). Secondly, on their cumulative effects (Equ. 31).

$$H_{\varepsilon_{g,q}}^{\text{int}}(z) = \frac{\left(1 - \varepsilon_{g,q}\right)^2 z^{-1}}{1 - \left(1 - \varepsilon_{g,q}\right)^2 z^{-1}}$$

(32)

$$H_{\varepsilon_s}^{\text{int}}(z) = \frac{\left(1 - \varepsilon_s\right)^2 z^{-1}}{1 - \left(2\varepsilon_s + \left(1 - \varepsilon_s\right)^2\right) z^{-1} + \varepsilon_s^2 z^{-2}}$$

(33)

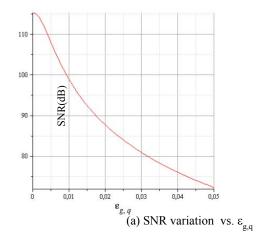

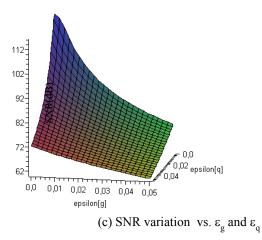

#### A. Effects on dynamic Performances

The ideal transfer function of the integrator presented in Figure 1 is replaced by the one given in Equ. 31, Equ. 32 or Equ. 33. Table 1 shows the simulation parameters. According to Equ. 4 to Equ. 6, for typical variations of the error parameters between  $\theta$  (the ideal case) and 5%, Figure 7 shows the *SNR* variation versus error mechanisms ( $\varepsilon_g$ ,  $\varepsilon_q$  and  $\varepsilon_s$ ).

Figure 7(a) and Figure 7(c) show respectively the separately and the cumulative effect of  $\varepsilon_g$  and  $\varepsilon_q$  on the modulator *SNR*. We notice that these errors have a big effect on the *SNR* and their variation destroys the benefits of the oversampling. Unlike, the settling time error  $\varepsilon_s$  has not a significant effect on the *SNR* since its variation is between 113 and 115 dB as shown in Figure 7(b).

Figure 7. SNR variation versus SI errors. (a) Influence of  $\epsilon_{g,q}$  (b) Influence of  $\epsilon_{s}$ . (b) Influence of  $\epsilon_{g}$  and  $\epsilon_{q}$ .

Table 1. Simulation Parameters

| Simulation parameters     | Value     |

|---------------------------|-----------|

| Oversampling Ratio (OSR)  | 278       |

| Sampling frequency (fs)   | 12.25 Mhz |

| Input Signal frequency(f) | 5.4 Khz   |

| Band of interest (Bw)     | 22.05 Khz |

| FFT samples number (N)    | 65536     |

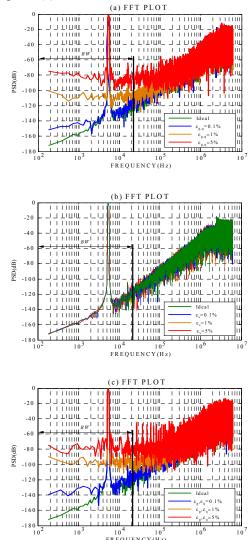

For the effect of these errors on the noise-shaping of  $\Sigma\Delta M$ , we perform a simulation of the modulator output Power Spectral Density (PSD). As shown in Figure 8(a) and Figure 8(c) the in-band noise increases when  $\varepsilon_g$  or/and  $\varepsilon_q$  increase. But in-band noise remains unchanged when  $\varepsilon_s$  increases as shown in Figure 8(b).

Figure 8. Output modulator Power Spectral Density. (a) PSD for typical value of  $\varepsilon_{g,q}$  (b) PSD for typical value of  $\varepsilon_s$ . (c) PSD for cumulative effect of  $\varepsilon_g$  and  $\varepsilon_q$

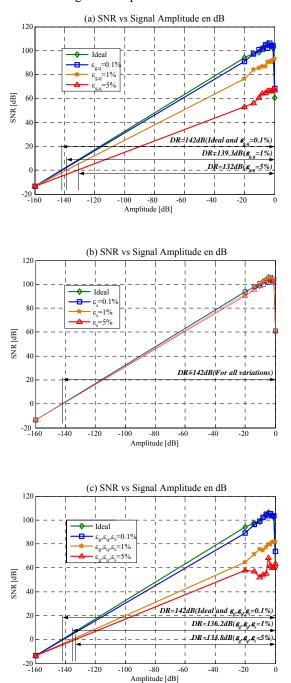

The <u>Dynamic Range</u> (DR) of the modulator is given by the difference between the maximum input amplitude and the input amplitude that gives an SNR equal to zero as shown in Figure 9. For  $\varepsilon_g$  or  $\varepsilon_q$  vary from 0% to 5%, DR decrease from 142 to 132dB. For the same variation of  $\varepsilon_s$ , DR remain unchanged and equal to 142dB.

Figure 9. SNR vs. Amplitude (dB). (a) For typical value of  $\epsilon_{g,q}(b)$  For typical value of  $\epsilon_{s}$ . (c) For cumulative effect of  $\epsilon_{g}$ ,  $\epsilon_{q}$  and  $\epsilon_{s}$ .

Table 2, Table 3 and Table 4 show respectively the effect of separately and cumulative SI-related errors on dynamic performances and then on the *ENOB*.

Table 2. Variation of dynamic performances for  $\varepsilon_{g,q}$ = 0.1%, 1% and 5%

| $\epsilon_{\mathrm{g,q}}$ | SNR (dB) | S_THD (dB) | ENOB (bits) |

|---------------------------|----------|------------|-------------|

| 0%(Ideal)                 | 106.33   | 103.54     | 17.38       |

| 0.1%                      | 101.96   | 104.82     | 16.65       |

| 1%                        | 90.41    | 91.25      | 14.74       |

| 5%                        | 66.71    | 64.08      | 10.80       |

Table 3. Variation of dynamic performances for  $\varepsilon_s$ = 0.1%, 1% and 5%

| $\epsilon_{\rm s}$ | SNR (dB) | S_THD (dB) | ENOB (bits) |

|--------------------|----------|------------|-------------|

| 0%(Ideal)          | 106.33   | 103.54     | 17.38       |

| 0.1%               | 101.61   | 104.42     | 16.59       |

| 1%                 | 104.32   | 106.57     | 17.05       |

| 5%                 | 104.91   | 105.71     | 17.14       |

Table 4. Variation of dynamic performances for  $\varepsilon_g$  and  $\varepsilon_q$ = 0.1%, 1% and 5%

| $\epsilon_{g}$ and $\epsilon_{q}$ | SNR (dB) | S_THD (dB) | ENOB (bits) |

|-----------------------------------|----------|------------|-------------|

| 0%(Ideal)                         | 106.33   | 103.54     | 17.38       |

| 0.1%                              | 102.71   | 100.85     | 16.78       |

| 1%                                | 80.02    | 78.81      | 13.01       |

| 5%                                | 61.03    | 55.40      | 9.85        |

# B. Effects on static performances

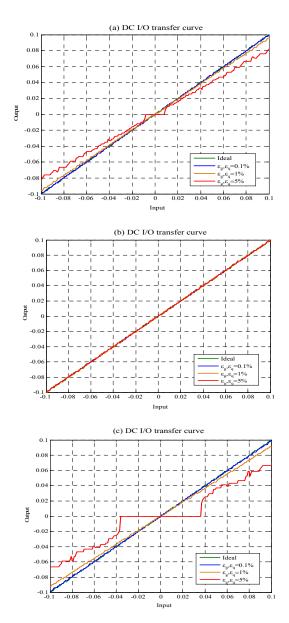

According to [28-30], when characterizing an imperfect modulator, we intend to find its DC offset and gain. The DC I/O transfer curve characterizes the non-ideal modulator better than the Integral/Differential non Linearity (INL/DNL). The output bit stream of an ideal modulator, for a rational DC input value x, is a series of repetitive patterns which the base one are called limit cycle. The average over a complete period is equal to x. As shown in Figure 10(b) the limit cycle is not affected when the settling time error  $\varepsilon_s$  vary. But, we notice that, from Figure 10(a) and Figure 10(c), the limit cycle is invariable in the range of input within [-0.01, 0.01] for separately variation of  $\varepsilon_g$  or  $\varepsilon_q$ . For cumulative effect, the limit cycle is constant for a range of input [-0.04, 0.04].

Figure 10. DC I/O modulator transfer curve. (a) For typical value of  $\varepsilon_{g,q}$  (b) For typical value of  $\varepsilon_s$ . (c) For cumulative effect of  $\varepsilon_g$  and  $\varepsilon_q$

### **Conclusions**

A behavioral study regarding to the non-idealities of SI memory cell has been detailed. This study has been extended to a higher level such as integrator and then modulator. An erroneous Non-inverting Lossless Integrator transfer function has been developed. The simulation results show the influence of these non idealities on the dynamic and static performances on the 2nd order SI-LP $\Sigma$ AM. We can conclude that I/O conductance ratio as well as charge injection errors have a remarkable effect on both dynamic and static performances. Unlike, settling time error has not a significant effect on the modulator output. Future work will be focused on test and calibration of the modulator in order to minimize the effect of these errors and improve performances of SI $\Sigma$ Ā-ADC.

#### References

- [1] R. Wilcock, and B. M. Al-Hashimi, "Analogue Filter IP Cores for Design Reuse". *IEE Conference on Analog Signal Processing, Oxford, UK. 2.1-2.6, Nov. 2002*

- [2] J. B. Hughes, K. W. Moulding, J. Richardson, J. Bennet, W. Redman-White, M. Bracey, and R.S. Soin, "Automated design of switched-current filters." *IEEE J. Solid-State Circuits*, vol. 31, pp. 898–907, July 1996.

- [3] C. Wang, "current-memory-based differentiator with protection of storage node", *Electron. Lett.*, vol. 34, pp. 1897-1898, Oct. 1998.

- [4] G. Fayolle and A. Kaiser, "Low-power hight-precision current memory integrator for analogue sigma-delta modulator", *Electron. Lett.*, vol. 34, pp. 1624-1625, 1998.

- [5] G. Sung, K. Chang, W. Lin, "A 12-B 10 msamples/s CMOS switched current delta-sigma modulator", *IEEE International Symposium on Circuits and Systems*, vol. 6, pp. 5573-5576, 2005.

- [6] R. Schreier, G. C. Temes, "Understanding Delta-sigma Data Converters", IEEE Press: New York, 2005.

- [7] S. R. Norsworthy, R. Schreier and G.C. Temes, "Delta Sigma Converters. Theory, Design and Simulation", IEEE Press: New York, 1997.

- [8] R. Zanbaghi, "Wide-Bandwidth, High-Resolution Delta-Sigma Analog-to-Digital Converters," *Oregon State University, Oregon, USA, Dissertation* 2011.

- [9] N. Tan, "Switched-Current Design and Implementation of Oversampling A/D Converters", *Kluwer Academic Publishers* 1997.

- [10] M. Voelker, J. Hauer, J. Sauerer, "Prospect of the future of switched-current circuits with regard to future CMOS technologies", *Microelectronics Journal*, Vol 39, pp. 286-292, 2008.

- [11] Toumazou, N. C. Battersby, "Switched-currents: An analogue Technique for digital technology", *Institution of Electrical Engineers, London, UK*, 1993.

- [12] J. B. Hughes, A. Worapishet, C. Toumazou, "Switched-capacitors versus switched-currents: a theoretical comparison", *IEEE International Symposium on Circuits and Systems*, Vol 2, Geneva, Switzerland, pp. 409-412. 2000

- [13] P. Snitala, A. S. Botha, "A/D converter based on a new memory cell implemented using the switched current technique", *Microelectronics Reliability* vol. 44, pp. 861-867, 2004.

- [14] C. Toumazou, J. B. Hughes, and N.C. Battersby, (Editors), "Switched- Currents: An Analogue Technique for digital technology", London: Peter Peregrinus Ltd., 1993.

- [15] R. van de Plassche: "Integrated analog-to-digital and digital-to-analog converters", *Kluwer Academic Publishers*, 1994.

- [16] N. Khitouni and M. Masmoudi, "Design of 2.5V second order sigma-delta modulator using regulated cascode S2I memory cell", *Journal of Electronics*, 94:7, 725 741, April 2007.

- [17] M. Loulou, N. Masmoudi, D. Dallet, L.Kamoun and Ph.Marchegay, "Behavioral Methodology to Simulate Switched Current Sigma-Delta Modulator", MED 2001, Dubrovnik: Croatie 2001.

- [18] A. Dei and M. Valle, "Modelling charge injection in MOS analogue switches using a compact model in a deep submicron technology", *IEE Proc.-Circuits Devices Syst.*, Vol. 153, No. 3, June 2006.

- [19] W. Ming Koe, J. Zhang, "Understanding The Effect Of Circuit Non-Idealities On Sigma-Delta Modulator", Proceedings of the 2002 IEEE International Workshop on Behavioral Modeling and Simulation (BMAS) 6-8 Oct. 2002.

- [20] A. Dendouga, N. Bouguechal, S. Kouda and S. Barra, "Modeling of a Second Order Sigma-Delta Modulator with Imperfections", *International Journal on Electrical Engineering and Informatics* - Volume 3, Number 2, 2011.

- [21] P. Malcovati, S. Brigati, F. Francesconi, F. Maloberti, P. Cusinato And A. Baschirotto. "Behavioral Modeling of Switched-Capacitor Sigma-Delta Modulators", in *IEEE Transactions on Circuits and Systems-I: Fundamental Theory and Applications*, Vol. 50, No. 3, pp. 352-364, Mar. 2003

- [22] S. J. Daubert, D. Vallancourt, and Y. P. Tsividis, "Current copier cells" *Electronics Letters*, pp. 1560–1562, Dec. 1988.

- [23] P. J. Crawley and G.W. Roberts, "Predicting harmonic distortion in switched-current memory circuits" *IEEE Trans. Circuits and System*, vol. 4, pp. 73–86, Feb. 1994.

- [24] J.M. Martins and V.F. Dias, "Harmonic distortion in switched current audio memory cells" *IEEE Transactions on Circuits and Systems II*, vol. 46, pp. 326–334, Mar. 1999.

- [25] J. M. De la Rosa, B. Péres-Verdu, F. Mederio, R. del Rio and A. Rodriguez-Vazquez, "Analysis of Error Mechanisms in Switched-Current Sigma-Delta Modulators", *Analog Integrated Circuits and Signal Processing*, vol 38, Issue 2-3, pp 175 - 201, 2004.

- [26] K. Abbes and M. Masmoudi, "A Theoretical Study of Error Mechanisms in Switched-Current Circuits", 3rd International Conference on Signals, Circuits and Systems (SCS), 6-8 Nov. 2009.

- [27] P.J. Crawley and G.W. Roberts, "Predicting Harmonic Distortion in Switched-Current Memory Circuits", IEEE trans. Circuits and Systems II, pp. 73-86, Feb. 1994.

- [28] K. Abbes, A. Hentati, M. Masmoudi, "Test And Characterization Of 1 Bit S D Modulator", 5th International Multi-Conference on Systems, Signals and Devices (SSD), 20-22 July 2008.

- [29] J.-L. Huang; K.-T. Cheng, "Testing and characterization of the one-bit first-order deltasigma modulator for on-chip analog signal analysis", *International Test Conference*,. p.p. 1021 – 1030, 03-05 Oct 2000

- [30] O. Feely and L. O. Chua. "The effect of integrator leak in Sigma-Delta modulation", *IEEE Trans. Circuits Syst*, vol. 38(11):1293-305, Nov. 1991.

**Karim ABBES** was born in Sfax, Tunisia, in 1979. He received the B. Sc in electrical Engineering from College of Sciences and Techniques, Tunis, Tunisia (ESSTT) in 2003 and the M. Sc in System on chip from the National Engineers School of Sfax, Sfax, Tunisia in 2005.

From 2005 to 2009, he was an Associate with the Faculty of Sciences, Sfax, Tunisia. Since 2010, he has been with the Private Polytechnic of Advanced Sciences Institute, Sfax, Tunisia. He is a member of the

Laboratory Electronics, Microtechnology and Communication.

His research interests include data conversion, analog/mixed-signal circuit design and test.

Naoufel Gueddah was born in Kairouan, Tunisia, in 1973. He received the Higher Diploma in Physical science Option Microelectronics from Faculty of Sciences of Monastir (FSM), Tunisia in 1997 and The Masters' degree in Electronics from Engineers School of Sfax, (ENIS), Tunisia, in 1999, and the Ph.D. degree in Electrical Engineering from ENIS, Tunisia, in 2010. His research interests include data conversion and analog/mixed-signal circuit design.

From 2003 to 2010, he was an Associate with the Faculty of Sciences of Sfax, Tunisia. Since 2011, he has been with the same Faculty as an Associate Professor. He is a member of the Laboratory Electronics, Microtechnology and Communication.

**Mohamed MASMOUDI** was born in Sfax, Tunisia, in 1961. He received the Engineer in electrical Engineering degree from the National Engineers School of Sfax, Sfax, Tunisia in 1985 and the PhD degree in Microelectronics from the Laboratory of Computer Sciences, Robotics and Microelectronics of Montpellier, Montpellier, France in 1989.

From 1989 to 1994, he was an Associate Professor with the National Engineers School of Monastir, Monastir, Tunisia. Since 1995, he has been

with the National Engineers School of Sfax, Sfax, Tunisia, where, since 1999, he has been a Professor engaged in developing Microelectronics in the engineering program of the university, and where he is also the Head of the Laboratory Electronics, Microtechnology and Communication. He is the author and co-author of several papers in the Microelectronic field. He has been a reviewer for several journals.

Dr. Masmoudi organised several international Conferences and has served on several technical program committees.